# **ST-NXP Wireless**

# **IMPORTANT NOTICE**

Dear customer,

As from August 2<sup>nd</sup> 2008, the wireless operations of STMicroelectronics have moved to a new company, ST-NXP Wireless.

As a result, the following changes are applicable to the attached document.

- Company name STMicroelectronics NV is replaced with ST-NXP Wireless.

- Copyright the copyright notice at the bottom of the last page "© STMicroelectronics 200x - All rights reserved", shall now read: "© ST-NXP Wireless 200x - All rights reserved".

- Web site <u>http://www.st.com</u> is replaced with <u>http://www.stnwireless.com</u>

- **Contact information** the list of sales offices is found at <u>http://www.stnwireless.com</u> under Contacts.

If you have any questions related to the document, please contact our nearest sales office. Thank you for your cooperation and understanding.

**ST-NXP** Wireless

18-bit Low Power Asynchronous Stereo Audio DAC with Integrated Power Amplifiers and Voice Codec

#### FEATURES

- Complete stereo audio digital to analog converters and filters

- 18-bit, 8 kHz to 48 kHz DAC with sample-rate conversion

- Linear phase analog&digital filters

- 16  $\Omega$  load stereo headphones drivers, 8  $\Omega$  load mono loudspeaker driver for group listening

- Stereo audio DAC features

- Asynchronous sampling DAC: does not require oversampled clock and information on the audio data sampling frequency. Jitter tolerant

- Multibit  $\Sigma\Delta$  modulator with data weighted averaging DAC

- 92 dB dynamic range, 0.01% THD over 16  $\Omega$  load performance

- Support any sampling frequency in the range 8 kHz to 48 kHz

- DSP functions for bass-treble-volume controls, deemphasis filter and dynamic compression

- Tones from tone generator can be injected in the audio paths

- Stereo headphones and loudspeaker/earpiece power amplifiers features and stereo input for FM radio features:

- 20 kHz bandwidth stereo headphones outputs. Driving capability: 40 mW (typ. 0.1% T.H.D) over 16 Ωwith 40 dB range programmable gain

- Balanced earpiece/ loudspeaker output.

Driving capability: 300 mW (typ. 0.1% T.H.D) over 8 Ω with 30dB range programmable gain

- Analog stereo input for FM radio with 38 dB range programmable gain

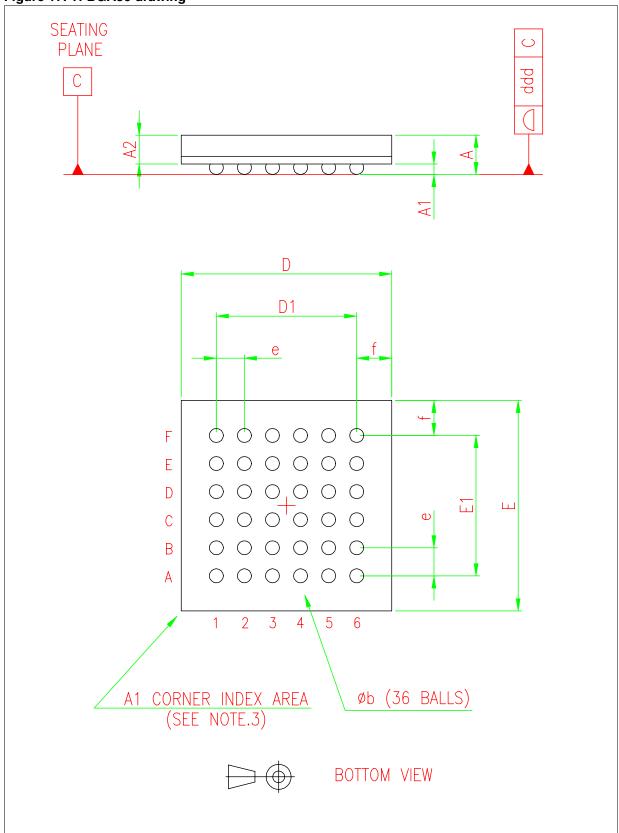

TFBGA 6x6 (36 pins) ORDER CODES: STw5094AD/LF, STw5094ADT/LF

- Complete CODEC and filter system

- 14-bit linear or 8-bit companded ADC and DAC

- Transmit and receive digital band-pass filters

- Active antialias and smoothing filters

- 8 Ω load earpiece/loudspeaker driver, 16 Ω load auxiliary driver

- Voice CODEC features

- Support 8 kHz or 16 kHz sampling rate

- One microphone biasing output

- Remote control function

- Three switchable microphone amplifier inputs. 42.5 dB range programmable gain

- Transient supression during power up and power down

- Internal programmable sidetone

- Internal ring, tone and dtmf generator

- Programmable PWM buzzer driver

- General features

- Single 2.7 V to 3.3 V supply

- Extended temperature range operation <sup>1</sup>

-40 °C to 85 °C

- 1  $\mu W$  standby power (typ. AT 2.7V).

- 16 mW operating power in audio listening mode (typ. at 2.7 V).

<sup>1.</sup>Functionality guaranteed in the range -40°C to +85°C; Timing and Electrical Spec. are guaranteed in the range -30°C to +85°C.

- 11 mW operating power in voice codec mode (typ. at 2.7 V).

- 1.8 V to 3.3 V CMOS compatible digital interfaces

- Programmable PCM interface

- I<sup>2</sup>C compatible control interface

- Programmable master/slave serial audio data input interface (I<sup>2</sup>S and other formats)

- Frequency programmable clock output

## APPLICATIONS

- CDMA,GSM,DCS1800,PCS1900,JDC digital cellular telephones with MP3 and FM radio stereo listening functions

- Portable devices with a stereo digital audio source and FM radio listening function

#### **GENERAL DESCRIPTION**

STw5094A is a low power asynchronous stereo audio DAC device with headphones amplifiers for high quality MP3 and FM radio listening. The STw5094A includes also an high performance low power combined PCM Codec/ filter tailored to implement the audio front-end functions required by low voltage low power consumption digital cellular terminals with added MP3 and FM radio listening.

The STw5094A registers are accessed through an  $I^2C$ -bus compatible interface.

The STw5094A asynchronous stereo audio DAC section is suited for MP3, or any other audio stereo source, listening. It supports any rate from 8 kHz to 48 kHz, can tolerate jitter on audio data and

does not requires an oversampled clock. The audio data serial interface can be master or slave, it is  $I^2S$  compatible and supports other standard serial interface formats. The internal D to A converters work with 18 bit input resolution.

The stereo headphones drivers can also be used for FM radio listening via an auxiliary stereo analog input. A loudspeaker driver can also be used for monophonic group listening.

The STw5094A voice Codec section can be configured either as a 14-bit linear or as an 8-bit companded PCM coder. The frame voice Codec sample rate can be either the standard 8 kHz value or the extended 16 kHz one.

In addition to the stereo audio DAC and Codec/ filfunctions. STw5094A includes ter а tone/ ring/ DTMF generator that can be used both in audio listening mode and in voice Codec mode, a sidetone generation, a buzzer driver output and a remote control function tailored to handle an external on-hook off-hook button. STw5094A Voice Codec fulfills and exceeds D3/ D4 and CCITT recommendations and ETSI requirements for digital handset terminals. The Stereo Audio DAC part fulfills and exceeds the requirements for MP3 quality and FM radio quality listening. Main applications include digital mobile phones with added low-power high-quality MP3 and / or FM radio listening features, or any battery powered equipment that requires Stereo Audio DAC with Headphones drivers.

#### **ORDER CODES**

| Part Number   | Description            |

|---------------|------------------------|

| STw5094AD/LF  | TFBGA 36 Tray          |

| STw5094ADT/LF | TFBGA 36 Tape and Reel |

# TABLE OF CONTENT

| PIN CONNECTIONS (TOP VIEW)                                                                                                                                                                                                                           | 4                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                                                                                             | 5                                |

| SIGNAL DESCRIPTION                                                                                                                                                                                                                                   | 6                                |

| FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                               | 8                                |

| PROGRAMMABLE REGISTERS                                                                                                                                                                                                                               | 15                               |

| TIMING DIAGRAMS                                                                                                                                                                                                                                      | 25                               |

| ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                             | 33                               |

| OPERATIVE SUPPLY VOLTAGES                                                                                                                                                                                                                            | 33                               |

| TIMING SPECIFICATIONS                                                                                                                                                                                                                                | 33<br>33                         |

| MCLK and AUXCLK timing                                                                                                                                                                                                                               | 34                               |

| Audio interface signals timing                                                                                                                                                                                                                       | 34                               |

| PCM interface timing                                                                                                                                                                                                                                 | 34                               |

| I2C bus control port timing                                                                                                                                                                                                                          | 35                               |

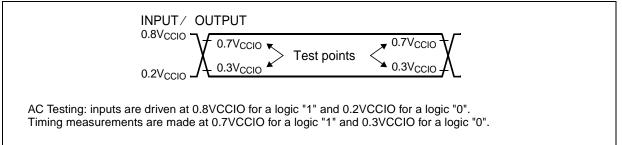

| ELECTRICAL CHARACTERISTICS<br>Digital Interfaces (Figure 16)                                                                                                                                                                                         | 36                               |

| Analog Interfaces                                                                                                                                                                                                                                    | 36                               |

| ANALOG INPUT/OUTPUT OPERATIVE RANGES<br>Microphone Input Levels - Absolute levels at MIC1, MIC2, MIC3<br>FM Input Levels - Absolute levels at FML, FMR<br>Power Output Levels - Absolute levels at LSP-LSN (Differentially measured)<br>Tones Levels | 37<br>37<br>37<br>37<br>37<br>37 |

| VOICE CODEC CHARACTERISTICS                                                                                                                                                                                                                          |                                  |

| VOICE CODEC AMPLITUDE RESPONSE                                                                                                                                                                                                                       | 38                               |

| VOICE CODEC AMPLITUDE RESPONSE (continued)                                                                                                                                                                                                           | 39                               |

| VOICE CODEC ENVELOPE DELAY DISTORTION WITH FREQUENCY                                                                                                                                                                                                 | 40                               |

| VOICE CODEC NOISE                                                                                                                                                                                                                                    | 40                               |

| VOICE CODEC CROSSTALK                                                                                                                                                                                                                                | 40                               |

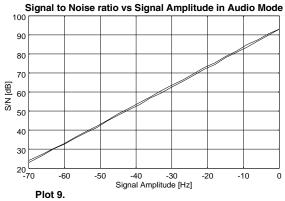

| VOICE CODEC DISTORTION                                                                                                                                                                                                                               | 41                               |

| VOICE CODEC DISTORTION                                                                                                                                                                                                                               | 42                               |

| STEREO AUDIO DAC and FM CHARACTERISTICS                                                                                                                                                                                                              | 43                               |

| POWER DISSIPATION                                                                                                                                                                                                                                    | 44                               |

| TFBGA PACKAGE OUTLINE                                                                                                                                                                                                                                | -                                |

| REVISION HISTORY                                                                                                                                                                                                                                     | 50                               |

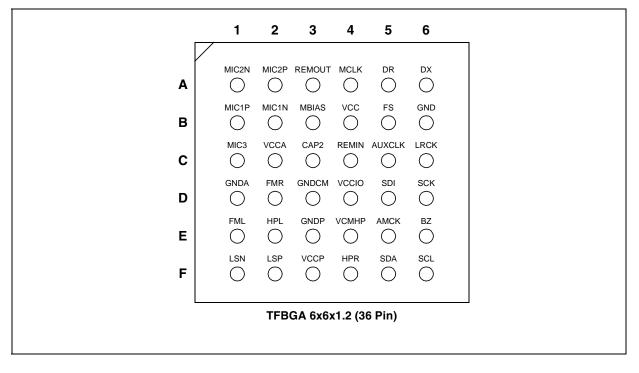

# **PIN CONNECTIONS (TOP VIEW)**

**\_\_\_**

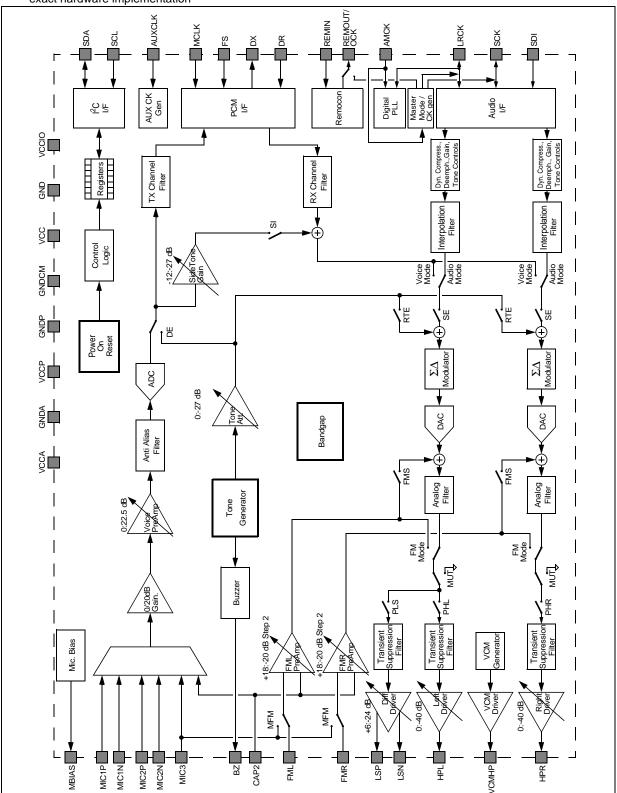

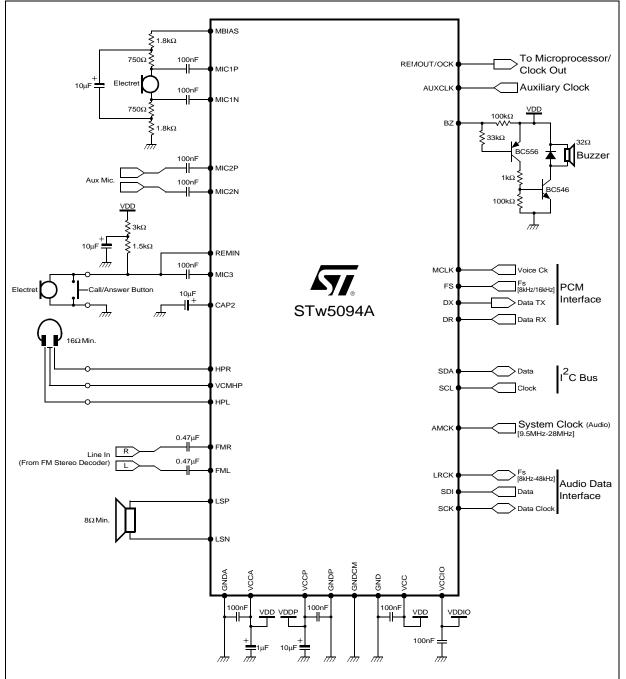

# FUNCTIONAL BLOCK DIAGRAM

57

Note: This diagram shows the functionality of the device and of some register bits but it does not necessarily reflect the exact hardware implementation

# SIGNAL DESCRIPTION

#### Type definitions:

AI - Analog input, AO - Analog Output, DI - Digital Input, DO - Digital output, DOT - Digital Output Tristate, DIOD - Digital Input Output Open Drain, DIOT - Digital Input Output Tristate, P - Power Supply or Ground.

| Pin N° | Name       | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B1     | MIC1P      | AI   | Positive high impedance input to transmit preamplifier for microphone 1 connection.                                                                                                                                                                                                                                                                                                                                                                        |

| B2     | MIC1N      | AI   | Negative high impedance input to transmit preamplifier for microphone 1 connection.                                                                                                                                                                                                                                                                                                                                                                        |

| A2     | MIC2P      | AI   | Positive high impedance input to transmit preamplifier for microphone 2 connection.                                                                                                                                                                                                                                                                                                                                                                        |

| A1     | MIC2N      | AI   | Negative high impedance input to transmit preamplifier for microphone 2 connection.                                                                                                                                                                                                                                                                                                                                                                        |

| C1     | MIC3       | AI   | High impedance single ended input to transmit preamplifier for microphone 3 connection. MIC3 can be used as monophonic input for the FM path in place of FML and FMR                                                                                                                                                                                                                                                                                       |

| B3     | MBIAS      | AO   | Microphone Biasing Switch.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| E1     | FML        | AI   | Auxiliary analog audio Left channel input.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| D2     | FMR        | AI   | Auxiliary analog audio Right channel input.                                                                                                                                                                                                                                                                                                                                                                                                                |

| F2,F1  | LSP, LSN   | AO   | Receive analog amplifier complementary outputs. This differential output can drive 50nF (with series resistor) or directly an earpiece transductor of $8\Omega$ The signal at this output can be: the sum of the Receive Speech signal from DR, FML (or MIC3) input, the Internal Tone Generator and the Sidetone signal, or the sum of the Audio Left channel, FML (or MIC3) input and the Internal Tone Generator, or can come from FML (or MIC3) input. |

| E2     | HPL        | AO   | Audio headphone amplifier Left channel output. This output can drive 50nF (with series resistor) or directly an earpiece transductor of $16\Omega$ The signal at this output can be the sum of Audio Left channel, FML (or MIC3) input and Internal Tone Generator, or the sum of Receive Speech signal from DR, FML (or MIC3) input, Internal Tone Generator, Sidetone signal, or can come from FML (or MIC3) input.                                      |

| F4     | HPR        | AO   | Audio headphone amplifier Right channel output. This output can drive 50nF (with series resistor) or directly an earpiece transductor of $16\Omega$ The signal at this output can be the sum of Audio Right channel, FMR (or MIC3) input and Internal Tone Generator, or the sum of Receive Speech signal from DR, FMR (or MIC3) input, Internal Tone Generator, Sidetone signal, or can come from FMR (or MIC3) input.                                    |

| A3     | REMOUT/OCK | DO   | Remocon function digital output / Oversampled Clock out.                                                                                                                                                                                                                                                                                                                                                                                                   |

| C4     | REMIN      | DI   | Remocon function input. A high level at this pin is detected as a non pressed key, while a low level is detected as a pressed key.                                                                                                                                                                                                                                                                                                                         |

| E6     | BZ         | AO   | Pulse width modulated buzzer driver output.                                                                                                                                                                                                                                                                                                                                                                                                                |

| F6     | SCL        | DI   | I2C-bus interface serial clock input. SCL is asynchronous with the other system clocks.                                                                                                                                                                                                                                                                                                                                                                    |

| F5     | SDA        | DIOD | I2C-bus interface serial data input-output.                                                                                                                                                                                                                                                                                                                                                                                                                |

| C6     | LRCK       | DIOT | Left / Right clock or Frame Sync for Audio interface input in Slave mode, output in Master mode.                                                                                                                                                                                                                                                                                                                                                           |

| D6     | SCK        | DIOT | Audio interface Serial Clock input in Slave mode, output in Master mode.                                                                                                                                                                                                                                                                                                                                                                                   |

| D5     | SDI        | DI   | Audio interface Data input.                                                                                                                                                                                                                                                                                                                                                                                                                                |

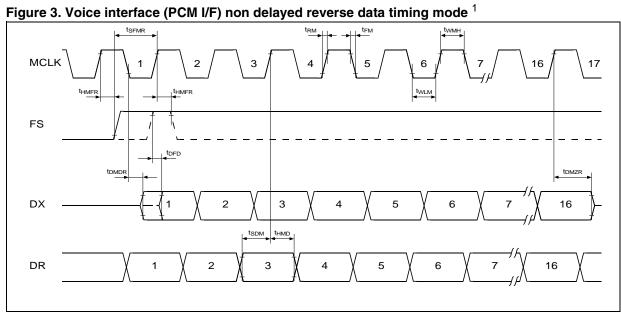

| E5     | АМСК       | DI   | Master Clock Input for Audio Mode. Can also be used as Master Clock in Tone Only and FM Modes.                                                                                                                                                                                                                                                                                                                                                             |

| Pin N° | Name   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A6     | DX     | DOT  | Transmit Data output: Data is shifted out on this pin during the assigned transmit time slots. Elsewhere DX output is in the high impedance state. In delayed and non-delayed normal frame sync modes, voice data byte is shifted out from tristate output DX at the MCLK frequency on the rising edge of MCLK, while in non-delayed reverse frame sync mode voice data is shifted out on the falling edge of MCLK. |

| A5     | DR     | DI   | Receive data input: Data is shifted in during the assigned Received time<br>slots In delayed and non-delayed normal frame sync modes voice data<br>byte is shifted in at the MCLK frequency on the falling edges of MCLK,<br>while in non-delayed reverse frame sync mode voice data byte is shifted<br>in on the rising edge of MCLK.                                                                              |

| B5     | FS     | DI   | Frame Sync input for Voice Mode: This signal is a 8/ 16kHz clock which defines the start of the transmit and receive frames. Any of three formats may be used for this signal: non delayed normal mode, delayed mode, and non delayed reverse mode.                                                                                                                                                                 |

| A4     | MCLK   | DI   | Master Clock Input for Voice Mode. Can also be used as Master Clock in Tone Only and FM Modes. The allowed clock frequencies are 512 kHz, 1.536 MHz, 2.048 MHz or 2.56 MHz. MCLK is the Voice Data Clock.                                                                                                                                                                                                           |

| C5     | AUXCLK | DI   | Auxiliary Clock Input. Can be used as Master Clock in Tone Only and FM Modes. Allowed clock frequencies are 512kHz, 1.536MHz, 2.048MHz or 2.56MHz.                                                                                                                                                                                                                                                                  |

| E4     | VCMHP  | AO   | VCM Driver Output. Can be used as common mode node for HPL and HPR outputs.                                                                                                                                                                                                                                                                                                                                         |

| C3     | CAP2   | AI   | A capacitor must be connected between this node and Ground.                                                                                                                                                                                                                                                                                                                                                         |

| C2     | VCCA   | Р    | Power supply input for the analog section. VCC and VCCA can be directly connected together for low cost applications.                                                                                                                                                                                                                                                                                               |

| D1     | GNDA   | Р    | Analog Ground: All analog signals are referenced to this pin. GND and GNDA can be connected together for low cost applications.                                                                                                                                                                                                                                                                                     |

| F3     | VCCP   | Р    | Power supply input for the output drivers.                                                                                                                                                                                                                                                                                                                                                                          |

| E3     | GNDP   | Р    | Power ground. Output drivers are referenced to this pin. GNDP and GNDA must be connected together.                                                                                                                                                                                                                                                                                                                  |

| D3     | GNDCM  | Р    | Analog Ground connection. GNDCM can be connected to GNDA.                                                                                                                                                                                                                                                                                                                                                           |

| B4     | VCC    | Р    | Power supply input for the digital section.                                                                                                                                                                                                                                                                                                                                                                         |

| B6     | GND    | Р    | Ground for the digital section                                                                                                                                                                                                                                                                                                                                                                                      |

| D4     | VCCIO  | Р    | Power supply Input for the Digital I/ O pins.                                                                                                                                                                                                                                                                                                                                                                       |

# FUNCTIONAL DESCRIPTION

# **1 DEVICE MODES**

STw5094A can work in 4 different modes, selected by bits **MD** in Control Register 21 (**CR21**). Depending on the mode different data interfaces, clock inputs, and internal blocks are selected. A built-in power consumption management function keeps in power down the blocks that are not needed by the selected operating mode. In all the modes the Output Drivers can be activated in different combinations with bits **PLS**, **PHL**, **PHR** in **CR6** (in case of stereo input and LSP/ N driver selected the Left channel is sent to this driver, while in case of voice input and **HPL** + **HPR** drivers selected the same signal is sent to both drivers).

#### 1.1 Audio Mode

In Audio mode the path from the Audio interface (Au I/ F) to the output drivers is active to allow the Stereo Audio DAC function. The Au I/ F is active while the PCM I/ F is inactive.

The master clock of the device is **AMCK**. The **AMCK** frequency is fixed, and independent from the audio samples data rate (**LRCK** frequency). **AMCK** source can be any fixed system clock whose nominal frequency value lies in the range 9.5MHz to 28MHz (the full range is covered in three sub-ranges, selected by bits **AMCK\_DIV** in **CR18**). The rate of the audio data (**LRCK** frequency) can be any value in the range 8kHz to 48kHz (non standard values are allowed) and does not need to be specified.

Since the **AMCK** clock is used directly in the D to A Converters section, its jitter and spectral properties must be adequate to the desired Audio quality.

In Audio Mode there are additional functions for audio signal processing:

- A digital volume control with 54 dB range is implemented (bits VOL in CR20). If the digital volume is

used in addition with the analog gain regulation a 94dB range volume is obtained.

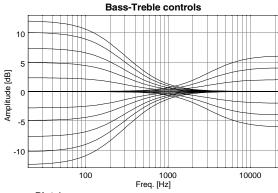

- Bass controls can be regulated in the -12.5dB to +12.5dB range in 2.5 dB step (bits **BASS** in **CR19**).

- Treble controls can be regulated in the -6dB to +6dB range in 2 dB step (bits TREBLE in CR19).

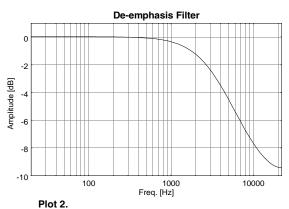

- The 50µs / 15µs de-emphasis filter is activated instead of treble controls (bits TREBLE in CR19). Note: the time constants are referred to the 44.1kHz FS.

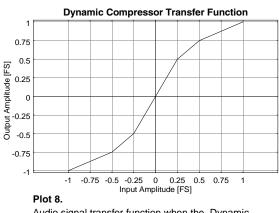

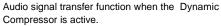

- A dynamic range compressor is implemented (bit CMP in CR20).

Note: The de-emphasis filter and the Bass/Treble controls freq. responses scale with the input sampling rate.

The tone/ ring/ DTMF generator can be activated if needed. In audio mode the frequency values of the tones is a function of the **AMCK** frequency value as explained in Table 1.

#### 1.2 Voice Mode

In Voice mode the TX path from microphone input to **DX** and the RX path from **DR** to the output drivers are active to allow the PCM CODEC function. The PCM I/ F is active while the Au I/ F is inactive. The master clock of the device is **MCLK**, the frequency of the clock can be selected with bits **F** in **CR0**. The tone/ ring/ DTMF generator can be activated if needed.

#### 1.3 Tone Only Mode

In tone only mode the path from the tone generator to the output drivers and to the buzzer is active to allow tones or ringer listening only. Both Au V F and PCM V F are inactive, as all the Audio and Voice converters functions.

The master clock of the device can be selected to be AUXCLK, MCLK or AMCK (bits CFM in CR21).

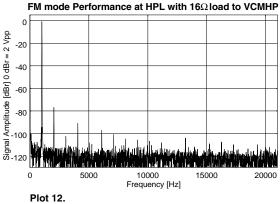

#### 1.4 FM Mode

8/51

In FM mode the path from **FML** and **FMR** analog inputs to the output Drivers is active to allow FM Stereo Radio listening. Both Au I/ F and PCM I/ F are inactive, as all the Audio and Voice converters functions. The master clock of the device can be selected to be **AUXCLK**, **MCLK** or **AMCK** (bits **CFM** in **CR21**). The Tone/ Ring/ DTMF generator is in power down.

# **2 DEVICE OPERATION**

#### 2.1 Power on Initialization, Software Reset

When power is first applied, the "power on reset" circuitry initializes STw5094A and puts it into the power down state. All the Registers are initialized as indicated in the Control Register description section. All the functions are disabled.

The registers can also be initialized to the default state by writing bit SRS (software reset) in CR21.

#### 2.2 Power up/ down control

It is recommended that all programmable functions (excluding the gain controls, bass-treble controls and dynamic compression function) are set while the device is powered down. Power state control can then be included in the last programming instruction (the power up bit **PU** is located in the last address register (**CR21**) so that the multi-byte mode of the control interface can be easily used to program all the required functions before power up).

When a power up command is given, all the circuits needed for the selected mode are activated (in Voice mode the **DX** output will remain in the high impedance state until the second **FS** pulse after power up arrives). A built-in power consumption management function keeps in power down the blocks that are not needed by the selected operating mode.

#### 2.3 Power down state

Following a period of activity, power down state may be reentered by writing 0 in bit **PU** in **CR21**. All the Control Registers remain in their current state and can be changed by I<sup>2</sup>C control interface.

In addition to the power down instruction, the detection of absence of the current Master Clock (no transition detected) automatically puts the device in power down state without setting bit **PU**. If transitions on the master clock are detected the device is put again in power up.

#### 2.4 Voice Transmit section

This section is active in Voice Mode. Voice Transmit analog preamplifier gain is designed in two stages to enable gains up to 42.5 dB. Stage 1 provides a selectable 0 or 20 dB gain via bit **PG** in **CR4**. Stage 2 is a programmable gain amplifier which provides from 0 to 22.5 dB of additional gain in 1.5dB step. It can be programmed with bits **TXA** in **CR4**. Three microphone inputs are provided, two differential (**MIC1P**/**N**, **MIC2P**/**N**) and one single ended (**MIC3**). They may also be used connect an auxiliary audio circuit. The microphone input or Transmit Mute is selected with bits **MS** in **CR4**. In the Mute case, the analog transmit signal is grounded. A separate **MBIAS** output can be used to bias a microphone (bit **MB** in **CR4**). An active anti-alias filter then precedes the single bit  $\Sigma\Delta$  analog to digital converter that is followed by an 8th order IIR digital TX channel filter. The TX channel filter is band-pass if the **FS** frequency is 8kHz and low-pass if the **FS** frequency is 16kHz (bit **VFS** in **CR0**). A precision on chip voltage reference ensures accurate and highly stable transmission levels. Any offset voltage arising in the analog blocks is cancelled by an internal autozero circuit. Voice data is sent to the PCM I/ F to be serially sent to **DX** output.

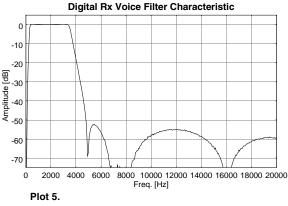

#### 2.5 Voice Receive section

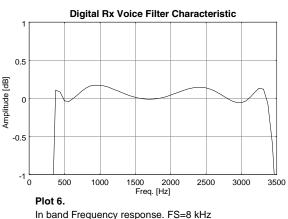

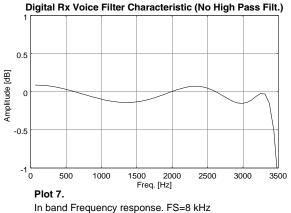

This section is active in Voice Mode. Voice Data coming from PCM I/ F **DR** pin is sent to the 8th order digital IIR RX channel filter. The filter can be selected to be band-pass or low-pass, with bit **HPB** in **CR5**, when **FS** frequency is 8kHz, while it is always low-pass when **FS** frequency is 16kHz. The filter is followed by a  $\Sigma\Delta$  digital to analog converter and a 3rd order switched-capacitor reconstruction filter. The Sidetone can be summed to the received signal (bit **SI** in **CR5**) and its amplitude can be programmed with bits **SA** in **CR5**.

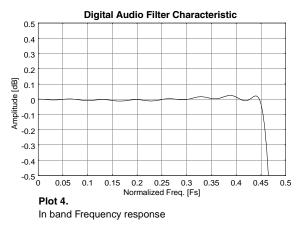

#### 2.6 Stereo Audio DAC section

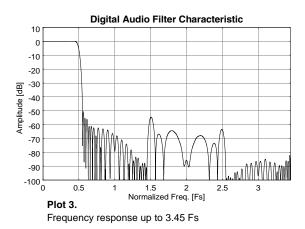

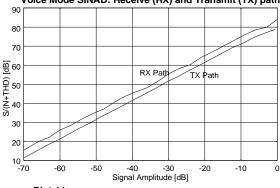

This section is active in Audio Mode. The Left and Right Audio samples coming from the Audio Interface are interpolated with an FIR filter and synchronized to the **AMCK** clock in order to feed the oversampled multi-bit  $\Sigma\Delta$  modulator, the digital to analog converter is followed by a 3<sup>rd</sup> order switched-capacitor reconstruction filter.

## 2.7 FM Input Path

The device is provided with stereo and mono single ended analog inputs, designed to amplify analog signals from an FM decoder but they can be considered as generic analog inputs. The stereo analog inputs are FML and FMR pins, or alternatively MIC3 pin for mono input (sent to left and right channels). The selection between FML-FMR or MIC3 is done with bit MFM in CR20.

The analog inputs are connected to a programmable gain stage that can amplify the signals in the range -20dB to +18dB in 2 dB steps. The gain control is independent for Left and Right channel and is selected with bits **FMLA** in **CR10** (Left) and bits **FMRA** in **CR11** (Right).

There are 2 ways to connect the FM inputs to the output drivers. The first is to select the FM Mode (bits **MD** in **CR21**). The second is to activate Audio or Voice or Tone Only modes and to set to 1 bit **FMS** in **CR20**. In the last case the signal coming from FM inputs will be summed to the Audio or Voice or Tones signals respectively.

#### 2.8 Output Drivers section

There are 3 Analog Output Drivers. The **LSP**/ **N** differential driver delivers 300mW typical power with 0.1% T.H.D. (250mW minimum undistorted) on a 8 $\Omega$  earpiece/ loudspeaker (piezoceramic loads up to 50nF can also be driven with a series resistor), it has a 30dB range gain control (bits **LSA** in **CR7**). The 2 single ended drivers (**HPL** and **HPR**) deliver 40mW typical power with 0.1% T.H.D. (30mW minimum undistorted) on 16 $\Omega$  stereo headphones, they have a 40dB range gain control (**CR8** for **HPL** and **CR9** for **HPR**). It is possible to put the drivers in power-down and in power-up by programming bits **PLS**, **PHL**, **PHR** in **CR6**. These settings are not dependent from the selected operative Mode.

The common mode voltage of all the drivers is selected with bits VCL in CR18 in the range 1.2V to 1.65V with 150mV steps. This feature is useful to set the common mode voltage to VCCP/2 and therefore to extend the output range and increase the output power.

If **HPL** and **HPR** are enabled together in Voice Mode or Tone Only Mode the same signal is sent to both Drivers. The active Drivers can be muted (keeping them in power-up state) using bit **MUT** in **CR6**. At power-up or after a change in **PLS** or **PHL** or **PHR** bits the outputs are muted for 10 ms to avoid unwanted noise. The transient suppression filter is used to avoid clicks when the gain value is changed.

#### 2.9 Common Mode Driver

The common mode voltage driver (VCMHP pin) simplifies the application for a stereo headset connection saving two decoupling capacitors in series with HPL and HPR. The loads of the single ended drivers are connected on one side to HPL and HPR respectively, and on the other to VCMHP, that has the same common mode voltage. The driver is enabled with bit VCE in CR18.

The output voltage of **VCMHP** is selected with bits **VCL** in **CR18** in the range 1.2V to 1.65V with 150mV steps.

#### 2.10 Tone Generator

The Tone Generator can be activated (writing **CR12**) in all the STw5094A operating modes except FM mode. In Voice and Audio modes the tones are summed to the signal. It is possible to generate 1 or 2 summed waveforms (either sinusoidal or square wave), their frequencies can be set in **CR13** for the first one (f1) and in **CR14** for the second one (f2) accordingly to the values listed in Table 1 if the active master clock is **MCLK** or **AUXCLK**. If the active master clock is **AMCK** the frequency values specified in Table 1 must be multiplied by a factor  $k_{fAMCK}$  that depends on the **AMCK** frequency value. The amplitude of the generated waveform can be regulated in **CR12** over a 33dB range. When both f1 and f2 are selected the amplitude of f1 and f2 are lowered by 5dB and 7dB respectively with respect to the amplitude of a single waveform. In this way the amplitude of the summed waveforms does not overload and there is a 2dB difference between f1 and f2 amplitude as required for DTMF generation. The Tone Generator output can be sent to the Voice Transmit section (in Voice Mode), to the Power amplifiers, possibly mixed with audio or voice, (in all the modes except FM mode) and to the buzzer output **BZ** (in all the modes except FM mode).

## 2.11 Buzzer Output

The output **BZ** is intended to drive a Buzzer, via an external BJT, with a squarewave pulse width modulated (PWM) signal. The frequency of the signal is stored in **CR13** (see Tone Generator section and Table 1 for frequency values). For some applications it is also possible to multiply this PWM signal with a squarewave signal having a frequency stored in **CR14**. The duty cycle of the buzzer output can be varied in **CR15** in order to change the buzzer volume. Maximum load for **BZ** is  $5k\Omega$  and 50pF

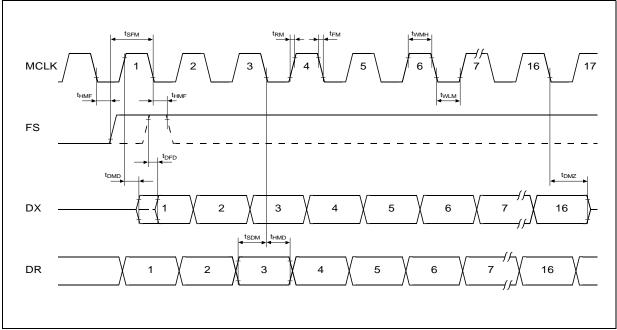

#### 2.12 Voice Data Interface (PCM // F)

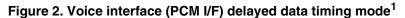

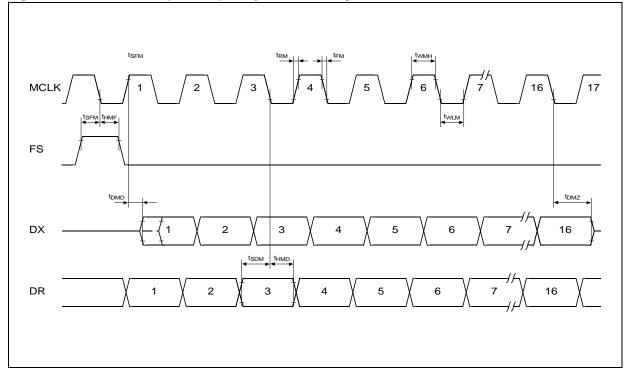

The PCM *V* F is used to exchange the Voice data in both TX and RX direction, it can be programmed for linear format data or companded A-law or  $\mu$ -law format (see Fig.1, 2 and 3).

Frame Sync input **FS** determines the beginning of frame. It may have any duration from a single cycle of **MCLK** to a squarewave. Three different relationships may be established between the Frame Sync input and the first time slot of the frame by setting bits **DM** in **CR1**. In non delayed normal and reverse data mode (long frame timing) the first time slot starts at the rising edge of FS. In delayed data mode (short frame sync timing) **FS** input must be high for at least a half cycle of **MCLK** before the frame start.

When linear code is selected (bit CM = 0 in CR0) the MSB is transmitted and received first, the word length is 16 bit. When companded code is selected (bit CM = 1 in CR0) a time slot assignment may be used in all timing modes (bit TS in CR1), that allows connection to one of the two B1 and B2 voice data channels. Two data formats are available: in Format 1, time slot B1 corresponds to the 8 MCLK cycles that immediately follow the rising edge of FS, while time slot B2 corresponds to the 8 MCLK cycles that immediately follow time slot B1. In Format 2, time slot B1 is identical to Format 1 while time slot B2 appears two bit slots after time slot B1. This two bits space is left available for insertion of the D channel data. Data format is selected by bit FF in CR0.

Bit EN in CR1 enables or disables data transfer on DX and DR.

Outside the selected time slot **DX** is in the high impedance condition. During the selected time slot the **DX** output and the **DR** input are synchronized as follow:

-If delayed or non-delayed modes are selected the transmit voice data is sent to **DX** output on the rising edges of **MCLK** and receive voice data is read at **DR** input on the falling edges of **MCLK**.

-If non-delayed reverse mode is selected the transmit voice data register is sent to **DX** output on the falling edges of **MCLK** and receive voice data is read at **DR** input on the rising edges of **MCLK**.

When 16kHz Frame Sync frequency is selected (bit VFS in CR0) the RX and TX filters are both low-pass and their cutoff frequencies are doubled.

It is possible to access the B channel data when companded A-law or  $\mu$ -law formats are used (bits **MX** and **MR** in **CR1**). A byte written into **CR3A** will be sent to **DX** output in place of the transmit channel PCM data. A byte written in **CR2A** will be sent to the receive path. The current byte received on **DR** input can be read in **CR2A**.

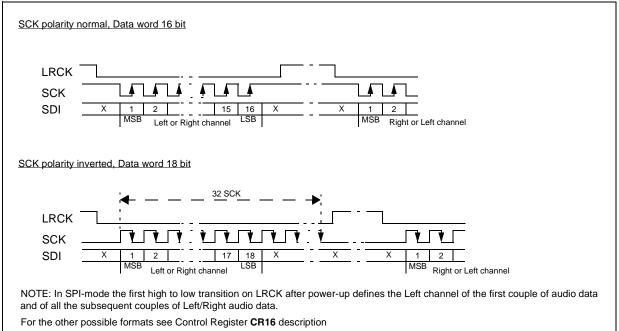

#### 2.13 Audio Data Interface (Au V F)

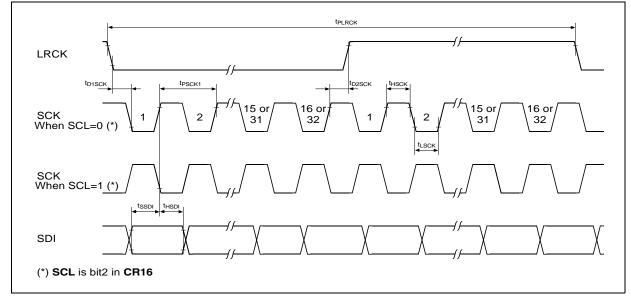

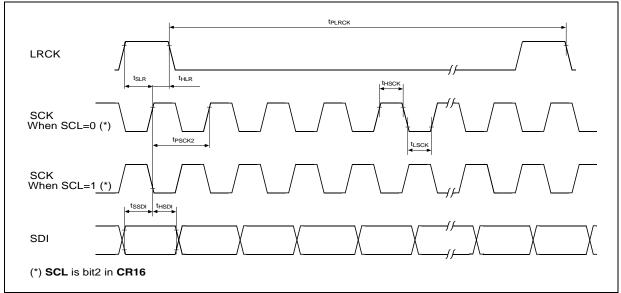

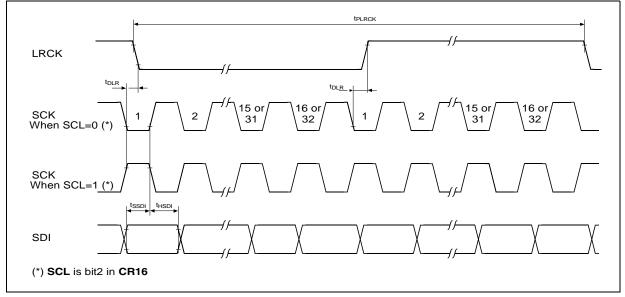

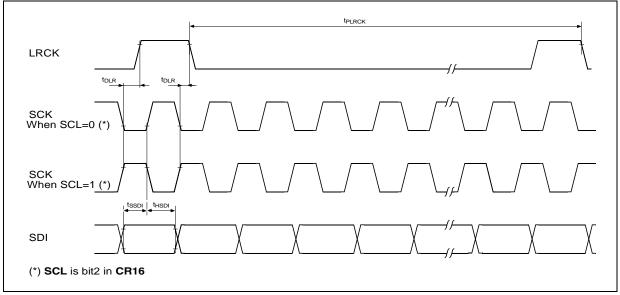

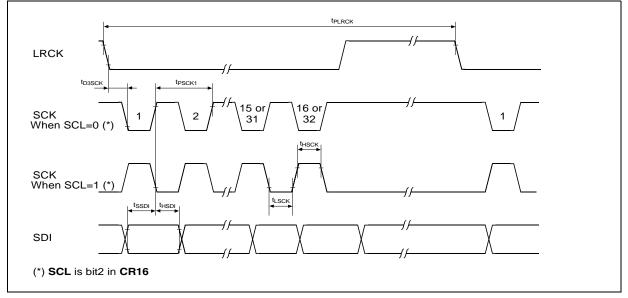

The Au V F is used to receive the Stereo Audio data. The pins related to the Au V F are: the frame synchronism or Left/Right indicator LRCK, the serial bit clock SCK, and the serial data input SDI. LRCK and SCK can be input or output depending if the Au V F is configured in Slave or Master mode.

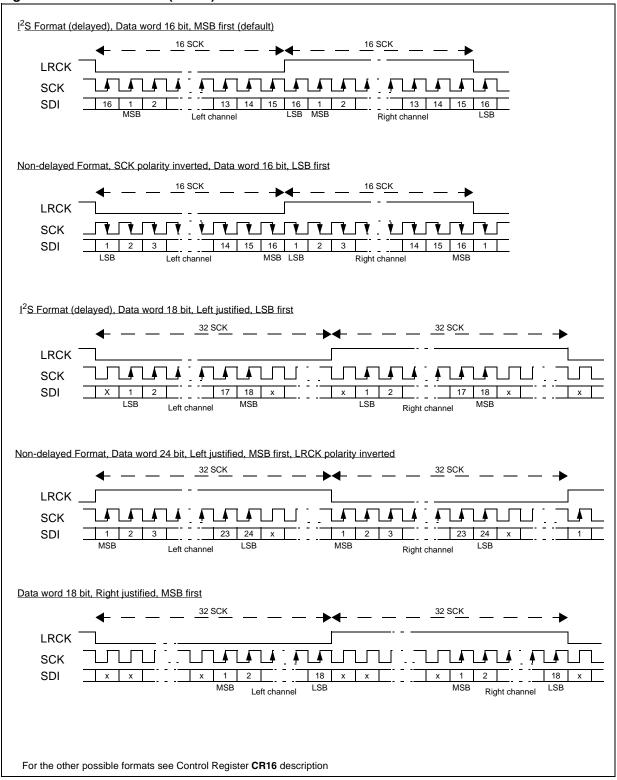

The interface can be configured in 5 different modes programming bits **SPIM**, **MSM** and **DSPM** in **CR17**. In each mode different parameters (word length, signal polarity etc.) can be set writing **CR16**.

The **MSM** bit selects if Au I/ F is Master or Slave. When **MSM**=0 the Au I/ F is Slave: the serial bit clock **SCK** and the frame sync **LRCK** are input to the device. When **MSM**=1 the Au I/ F is Master: **SCK** and **LRCK** are generated inside the device. The frequency of **LRCK** is programmed in **CR2B** and **CR3B** while its shape and the frequency of **SCK** change automatically with the selected mode (see paragraph below). Master mode is not available when the Au I/ F is configured in SPI-mode (**SPIM**=1) regardless of the value of **MSM**.

The 5 possible mode modes are:

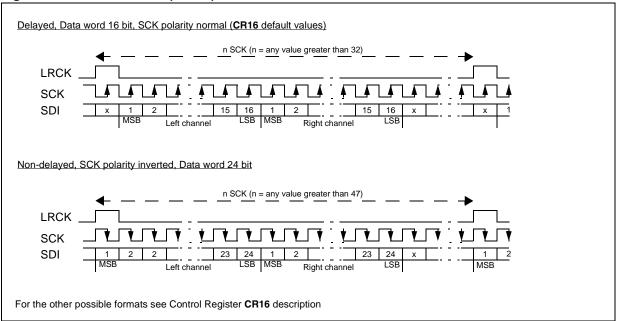

**I<sup>2</sup>S-Mode Slave** (SPIM=0, MSM=0 and DSPM=0) in this mode the Au I/ F is I<sup>2</sup>S compatible (see Fig. 5 and 10) and the bit clock SCK and the left/right indicator LRCK signals are input to the device. SCK must have 16 periods per channel in case of 16bit data word and 32 periods per channel in case of 18bit to 24bit data word. SCK can be either a continuous clock or a sequence of bursts.

# STw5094A

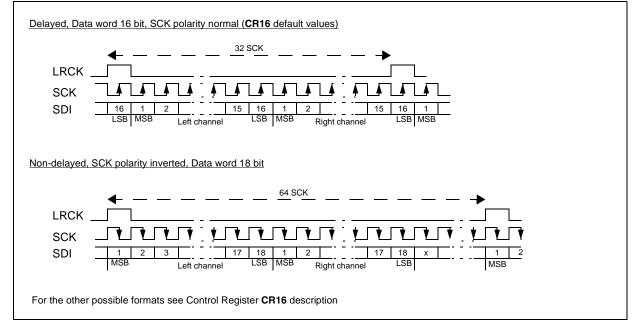

I<sup>2</sup>S-Mode Master (SPIM=0, MSM=1 and DSPM=0) this mode is functionally equivalent to I<sup>2</sup>S-mode Slave (see Fig. 7 and 10) but the bit clock SCK and the left/right indicator LRCK signals are generated by the device. SCK is generated with 16 periods per channel in case of 16bit data word and 32 periods per channel in case of 18bit to 24bit data word

**DSP-Mode Slave (SPIM=0, MSM=0** and **DSPM=1)** in this mode the Au I/ F starting from a frame sync pulse on **LRCK** receives the Left and Right data one after the other (see Fig. 6 and 11). **SCK** is a free running bit clock: between 2 successive frame sync pulse there can be any number of SCK periods from the minimum necessary to transfer all the data bits up to the max. frequency limit specified for **SCK**. DSP-mode is suited to interface with a Master Multi-Byte Serial Interface.

**DSP-Mode Master** (**SPIM**=0, **MSM**=1 and **DSPM**=1) this mode is functionally equivalent to DSP-mode Slave but **LRCK** and **SCK** signals are generated by the device (see Fig. 8 and 12). **SCK** is generated with 32 periods per frame sync. in case of 16bit data word and 64 periods per frame sync. in case of 18bit to 24bit data word. DSP-mode Master is suited to interface with a Slave Multi-Byte Serial Interface.

**SPI-Mode** (**SPIM**=1 and **DSPM**=0) in this mode Left and Right data are received with separate data burst. Every burst is identified with a low level on **LRCK** signal (see Fig. 9 and 13). There is no timing difference between the Left and Right data burst: the two channels are identified by the fact that the first burst after Audio mode power-up identifies the Left channel data and the second one is the Right channel data and then Left and Right data repeat one after the other. **SCK** must have 16 periods per channel in case of 16bit data word and 32 periods per channel in case of 18bit to 24bit data word. SPI-mode can only be Slave: when **SPIM**=1 the values written on **MSM** is disregarded while **DSPM** must be set to 0.

In some of the above listed modes not all the combinations of the bits in CR16 are available or meaningful:

- In DSP-Mode MSB is always received first (bit **ORD**=0), data word justification and **LRCK** polarity have no meaning.

- In SPI-mode the data word must be always left-justified (bit **DIF**=0) and non-delayed (bit **FOR**=1) and **LRCK** polarity must be always set for Left=0 (**INV**=0).

The audio data sample rate (**LRCK** frequency) can be any value in the range 8kHz to 48kHz. Left channel data are always received first.

The first 35 Data frames after power up are discarded while the interpolation filters data memory is cleared.

#### 2.14 LRCK & SCK generation in Master Mode

Setting **MSM**=1 and **SPIM**=0 in **CR17** enables the internal generation of the frame synchronism clock **LRCK** and of the serial bit clock **SCK**.

These clocks are obtained by variable division from the **AMCK** system clock. Given the **AMCK** frequency ( $f_{AMCK}$ ), the desired sample rate frequency ( $f_{LRCK}$ ) is obtained by writing in **CR2B** the least significant byte and in **CR3B** the most significant byte of the16bit integer result calculated with the following formula:

$N = round(2^{23} \cdot (f_{LRCK} / f_{AMCK}))$

The precision of the obtained  $f_{LRCK}$  is always better than ±1.7Hz.

The shape of LRCK waveform and the number of SCK periods for each LRCK period is set automatically depending on the values of bit DSPM in CR17 and of CR16 content (see Fig. 7,8,10 and 12).

Since **CR2B** and **CR3B** are overlaid registers, In order to write the division factor N in **CR2B** and **CR3B** the master mode must be selected in advance by setting **MSM**=1.

**NOTE: LRCK** and **SCK** are part of the Au  $I \neq F$ , but Master mode generation can also be used as Frame Sync and Master clock in Voice Mode by connecting them to **FS** and **MCLK** (in this case a fixed clock on **AMCK** is needed).

**Example:** The master clock frequency is  $f_{AMCK}=12MHz$ , the required sampling frequency is  $f_{L-RCK}=44.1kHz$ , N value is:

$$N = round(2^{23} \cdot (44100/ 1200000)) = 30828$$

30828 decimal corresponds to 786C hex so **CR2B** and **CR3B** must be loaded with 6C hex and 78 hex respectively, the frequency of **LRCK** will then be:

$f_{LRCK} = (30828.12000000 \text{ Hz})/2^{23} = 44099.8 \text{ Hz}.$

#### 2.15 OCK output clock generation

Setting OCE = 1 and SPIM = 0 in CR17 enables the internal generation of the clock OCK on the pin REMOUT / OCK. The clock output can be used as master clock for a digital device that provides the Audio Data to STw5094A.

This function is compatible with both Master mode and Slave mode of the **Au** I / F and can be used in Normal mode and in DSP mode while it cannot be used in SPI mode. It can be activated also in Voice mode (provided the **AMCK** clock is available).

Because **OCK** clock is obtained by variable division from the master clock **AMCK**, **OCK** cannot have a frequency higher than the **AMCK** master clock frequency.

When **OCK** frequency is comprised between **AMCK** frequency and half the **AMCK** frequency **OCK** is obtained removing pulses, as evenly spaced as possible, from **AMCK** and thus reducing the frequency to the programmed value. When **OCK** frequency is lower than half **AMCK** frequency it is obtained by division on the rising edge of **AMCK**.

**OCK** polarity can be inverted setting **ROI**=1 in **CR17**.

**OCK in Master Mode:** when the **Au I**/ **F** is used in Master Mode the **OCK** frequency is 256 times the sampling frequency programmed in **CR2B** and **CR3B** using the formula described in Section 2.14 ( $f_{OCK} = 256 \cdot f_{LRCK}$ ).

**OCK in Slave Mode:** when the **Au I**/ **F** is used in Slave Mode the **OCK** frequency can be set to any value (lower than **AMCK** frequency) and it is not related to the incoming **LRCK** frequency, then not limited to 256 oversampling. In this case to obtain the desired **OCK** frequency the following formula can be used:

$$N = round(2^{15} \cdot (f_{OCK} / f_{AMCK}))$$

where  $f_{OCK}$  is lower than  $f_{AMCK}$  (this corresponds to the fact that *N* cannot be greater than 7FFF hex). **Example:** The master clock frequency is  $f_{AMCK}=19.2$ MHz, the oversampling factor is 384 and the sampling rate is 44.1 kHz, then the required **OCK** frequency is  $f_{OCK} = 384 \cdot 44.1$  kHz = 16934400 Hz.

The value of N is:

28901 decimal corresponds to 70E5 hex so **CR2B** and **CR3B** must be loaded with E5 hex and 70 hex respectively, the frequency of **OCK** will then be

$$f_{OCK} = (28901 \cdot 19200000 \text{ Hz}) / 2^{15} = 16934179.7 \text{ Hz} = 384 \cdot 44099.4 \text{ Hz}$$

The **OCK** output clock function is alternative to the Remocon function because both share the same output pin: setting **OCE** = 1 will disable the Remocon function on the **REMOUT** / **OCK** but the REMOCON output status will still be available reading bit **RDL** in **CR17** (see paragraph II.18 for more details on REMO-CON function).

Since **CR2B** and **CR3B** are overlaid registers, in order to write the division factor N in **CR2B** and **CR3B**, the output clock function must be selected in advance by setting **OCE** = 1.

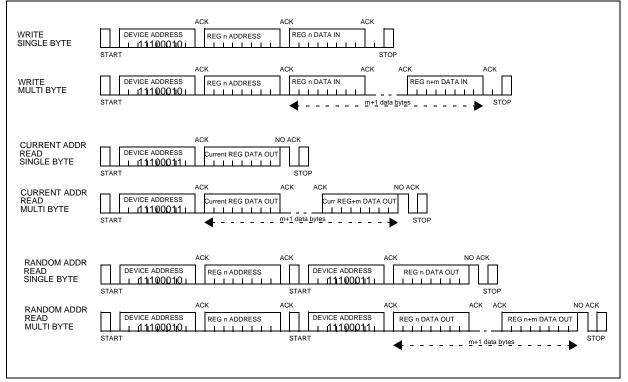

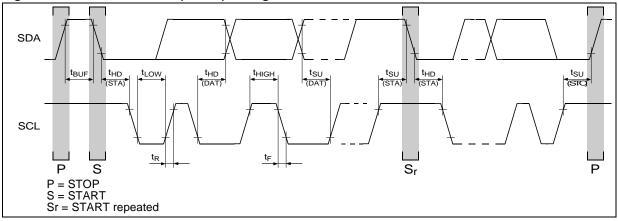

# 2.16 Control Interface (I<sup>2</sup>C V F)

The  $I^2C I/F$  is used to program the device by writing and reading the control registers (see Fig. 14 and 15). The interface is  $I^2C$  bus compatible, being the STw5094A a Slave device. **SDA** is the bidirectional open-drain data pin and **SCL** is the input clock pin. The Device Address is E2 hex. for writing and E3 hex. for reading.

The interface has an internal address register that keeps the current address of the control register to be read or written. At each write access of the interface the address register is loaded with the data of the register address field. The value in the address register is increased after each data byte read or write. It is possible to access the interface in 2 modes: single-byte mode in which the address and data of a single register are specified, and multi-byte mode in which the address of the first register to be written or read is specified and all the following bytes exchanged are the data of successive address register 0 after the last register 21). Using the multi-byte mode it is possible to write or read all the registers with a single access to the device on the  $I^2C$  bus.

The Control interface can be used both in power-up and power-down state.

#### 2.17 Master clock in FM mode and tone only modes

In FM mode and in Tone Only mode the Master Clock of the device can be selected to be **AUXCLK**, **MCLK** or **AMCK** writing bits **CFM** in **CR21**. The Auxiliary clock **AUXCLK** can be used when the Audio mode clock **AMCK** and the Voice mode clock **MCLK** are not available. **AUXCLK** and **MCLK** frequency selection is done with bits **F** in **CR0**.

#### 2.18 REMOCON function

The REMOCON (Remote Control) function can be used to detect the status of an headset button. The REMOCON function is enabled by setting bit **REN** in **CR17**. If enabled, this function is active also when the STw5094A is in power-down state. The **REMOUT/OCK** pin is the output pin for the REMOCON function only if **OCE** = 0 in **CR17** (Section 2.15).

A High level at **REMIN** input is detected as a non pressed button, while a low level is detected as a pressed button. The "Pressed Button" information can be treated in 2 ways depending on bit **RLM** in **CR17**:

- -if **RLM** = 0 (Transparent mode) the information at **REMIN** is seen at **REMOUT/OCK** after a debounce time of 50ms maximum;

- -if **RLM** = 1 (Latched Mode) the information stored in bit **RDL** in **CR17** is seen at **REMOUT/OCK**. **RDL** is set after a debounce time of 50ms maximum when a low level at **REMIN** is detected. **RDL** is reset with power on initialization and can also be reset writing 0 in bit **RDL**.

5/

The **REMOUT/OCK** output polarity can be inverted setting bit **ROI** in **CR17**: the pressed button information is presented at **REMOUT/OCK** output as a logic 1 if bit **ROI** = 0. If **ROI** = 1 the polarity is inverted.

# **PROGRAMMABLE REGISTERS**

#### Control Register CR0 Functions (Address: 0x00)

| 7                | 6                | 5      | 4      | 3                | 2                | 1      | 0      |                                                                                                                      | Function                                                                                               |  |

|------------------|------------------|--------|--------|------------------|------------------|--------|--------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| F(1              | :0)              | VFS    | СМ     | MA               | IA               | FF     | B7     |                                                                                                                      | T unction                                                                                              |  |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |        |        |                  |                  |        |        | MCLK or AUXCLK = 512 kHz *<br>MCLK or AUXCLK = 1.536 MHz<br>MCLK or AUXCLK = 2.048 MHz<br>MCLK or AUXCLK = 2.560 MHz |                                                                                                        |  |

|                  |                  | 0<br>1 |        |                  |                  |        |        | Voice Data Fs is 8 kHz<br>Voice Data Fs is 16 kHz                                                                    | *                                                                                                      |  |

|                  |                  |        | 0<br>1 |                  |                  |        |        | Linear code<br>Companded code                                                                                        | *                                                                                                      |  |

|                  |                  |        |        |                  |                  |        |        | Linear Code                                                                                                          | Companded Code                                                                                         |  |

|                  |                  |        |        | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |        |        | 2-complement *<br>sign and magnitude<br>2-complement<br>1-complement                                                 | μ-law: CCITT D3-D4 *<br>μ-law: Bare Coding<br>A-law including even bit inversion<br>A-law: Bare Coding |  |

|                  |                  |        |        |                  |                  | 0<br>1 |        | B1 and B2 consecutive<br>B1 and B2 separated                                                                         | (1) *<br>(1)                                                                                           |  |

|                  |                  |        |        |                  |                  |        | 0<br>1 | 8 bits time-slot<br>7 bits time-slot                                                                                 | (1) *<br>(1)                                                                                           |  |

(1): significant in companded mode only \*: state at power on initialization

## Control Register CR1 Functions (Address: 0x01)

| 7           | 6           | 5 | 4      | 3      | 2      | 1      | 0      | Function                                                                                                            |

|-------------|-------------|---|--------|--------|--------|--------|--------|---------------------------------------------------------------------------------------------------------------------|

| DM          | (1:0)       |   | MR     | МХ     | EN     | TS     | DL     | i unction                                                                                                           |

| 0<br>1<br>1 | X<br>0<br>1 |   |        |        |        |        |        | delayed data timing *<br>non-delayed normal data timing<br>non-delayed reverse data timing                          |

|             |             | Х |        |        |        |        |        |                                                                                                                     |

|             |             |   | 0<br>1 |        |        |        |        | D <sub>R</sub> connected to RX path *<br>CR2A connected to RX path (1)                                              |

|             |             |   |        | 0<br>1 |        |        |        | $ \begin{array}{c} \text{TX path connected to } D_X & & \ast \\ \text{CR3A connected to } D_X & & (1) \end{array} $ |

|             |             |   |        |        | 0<br>1 |        |        | PCM I/F disabled *<br>PCM I/F enabled                                                                               |

|             |             |   |        |        |        | 0<br>1 |        | B1 channel selected *<br>B2 channel selected (1)                                                                    |

|             |             |   |        |        |        |        | 0<br>1 | Normal operation *<br>Digital Loopback (Data from DR is sent to DX with 1 frame delay)                              |

(1) significant in companded mode only\*: state at power on initialization

X: reserved: write 0

#### Control Register CR2A Functions (Address: 0x02) (Active when MSM=0 and OCE=0 in CR17)

| 7   | 6       | 5 | 4   | 3     | 2 | 1 | 0   | Function                                                     |  |  |

|-----|---------|---|-----|-------|---|---|-----|--------------------------------------------------------------|--|--|

|     |         |   | DRD | (7:0) |   |   |     | r unction                                                    |  |  |

| msb | msb Isb |   |     |       |   |   | lsb | Data sent to Receive path or Data received from DR input (1) |  |  |

(1) Significant in companded mode only. CR2A is available only if Master mode and OCK out in CR17 are not enabled (MSM=0 and OCE=0).

#### Control Register CR2B Functions (Address: 0x02) (Active when MSM=1 or OCE=1 in CR17)

| 7   | 6 | 5 | 4    | 3      | 2 | 1 | 0   | Function                                                                                       |  |

|-----|---|---|------|--------|---|---|-----|------------------------------------------------------------------------------------------------|--|

|     |   |   | DIVL | .(7:0) |   |   |     |                                                                                                |  |

| msb |   |   |      |        |   |   | lsb | Least significant byte of the frequency division factor<br>for LRCK,SCK and OCK generation.(1) |  |

(1) CR2B is available only if the Master mode or OCK out in CR17 are enabled (MSM=1 or OCE=1, and SPIM=0).

#### Control Registers CR3A Functions (Address: 0x03) (Active when MSM=0 and OCE=0 in CR17)

| 7   | 6 | 5 | 4   | 3     | 2 | 1 | 0   | Function                |  |  |

|-----|---|---|-----|-------|---|---|-----|-------------------------|--|--|

|     |   |   | DXD | (7:0) |   |   |     | runction                |  |  |

| msb |   |   |     |       |   |   | lsb | DX data transmitted (1) |  |  |

(1) Significant in companded mode only. CR3A is available only if Master mode and OCK out in CR17 are not enabled (MSM=0 and OCE=0).

#### Control Registers CR3B Functions (Address: 0x03) (Active when MSM=1 or OCE=1 in CR17)

| 7   | 6 | 5 | 4    | 3     | 2 | 1 | 0   | Function                                                                                 |     |  |  |  |

|-----|---|---|------|-------|---|---|-----|------------------------------------------------------------------------------------------|-----|--|--|--|

|     |   | _ | DIVH | (7:0) | _ |   | _   | Function                                                                                 |     |  |  |  |

| msb |   |   |      |       |   |   | lsb | Most significant byte of the frequency division factor for LRCK, SCK and OCK generation. | (1) |  |  |  |

(1) CR3B is available only if the Master mode or OCK out in CR17 are enabled (MSM=1 or OCE=1, and SPIM=0).

#### Control Register CR4 Functions (Address: 0x04)

| 7                | 6                | 5      | 4      | 3                | 2                | 1                | 0                | Function                                                                                                                                 |

|------------------|------------------|--------|--------|------------------|------------------|------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| MS(              | (1:0)            | MB     | PG     |                  | ТХА              | (3:0)            |                  |                                                                                                                                          |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |        |        |                  |                  |                  |                  | Transmit input muted *<br>MIC1 Selected<br>MIC2 Selected<br>MIC3 Selected                                                                |

|                  |                  | 0<br>1 |        |                  |                  |                  |                  | MBIAS output disabled *<br>MBIAS output enabled                                                                                          |

|                  |                  |        | 0<br>1 |                  |                  |                  |                  | 20dB preamplifier gain *<br>0dB preamplifier gain                                                                                        |

|                  |                  |        |        | 0<br>0<br>-<br>1 | 0<br>0<br>-<br>1 | 0<br>0<br>-<br>1 | 0<br>1<br>-<br>1 | 0 dB Transmit Amplifier gain *<br>1.5 dB Transmit Amplifier gain<br>Transmit Amplifier in 1.5 dB step<br>22.5 dB Transmit Amplifier gain |

\*: state at power on initialization

# Control Register CR5 Functions (Address: 0x05)

| 7 | 6 | 5      | 4      | 3                | 2                | 1                | 0                | Function                                                                                                 |       |

|---|---|--------|--------|------------------|------------------|------------------|------------------|----------------------------------------------------------------------------------------------------------|-------|

|   |   | HPB    | SI     |                  | SA               | (3:0)            |                  |                                                                                                          |       |

| Х | Х |        |        |                  |                  |                  |                  |                                                                                                          |       |

|   |   | 0<br>1 |        |                  |                  |                  |                  | Voice Codec Receive High Pass filter enabled<br>Voice Codec Receive High Pass filter disabled            | (1) * |

|   |   |        | 0<br>1 |                  |                  |                  |                  | Voice Codec internal sidetone disabled<br>Voice Codec internal sidetone enabled                          | *     |

|   |   |        |        | 0<br>0<br>-<br>1 | 0<br>0<br>-<br>1 | 0<br>0<br>-<br>1 | 0<br>1<br>-<br>1 | -12.5 dB Sidetone gain<br>-13.5 dB Sidetone gain<br>Sidetone gain in 1 dB step<br>-27.5 dB Sidetone gain | *     |

(1): Valid only when Voice Data Fs=8kHz (VFS=0). When Voice data Fs=16kHz (VFS=1) The High Pass Filter is always disabled. \*: state at power on initialization

X: reserved: write 0

#### Control Register CR6 Functions (Address: 0x06)

| 7 | 6 | 5      | 4      | 3      | 2      | 1      | 0      | Function                                                                                             |   |

|---|---|--------|--------|--------|--------|--------|--------|------------------------------------------------------------------------------------------------------|---|

|   |   | MUT    | PLS    | PHL    | PHR    | SE     | RTE    | Function                                                                                             |   |

| Х | Х |        |        |        |        |        |        |                                                                                                      |   |

|   |   | 0<br>1 |        |        |        |        |        | The active output Drivers are operative<br>The active output Drivers are muted                       | * |

|   |   |        | 0<br>1 |        |        |        |        | LSP/ N output Driver is in power down<br>LSP/ N output Driver is in power up.                        | * |

|   |   |        |        | 0<br>1 |        |        |        | HPL output Driver is in power down<br>HPL output Driver is in power up                               | * |

|   |   |        |        |        | 0<br>1 |        |        | HPR output Driver is in power down<br>HPR output Driver is in power up                               | * |

|   |   |        |        |        |        | 0<br>1 |        | Audio or Voice Codec Signal to LS or HP disabled<br>Audio or Voice Codec Signal to LS or HP enabled. | * |

|   |   |        |        |        |        |        | 0<br>1 | Ring / Tone to LS or HP disabled<br>Ring / Tone to LS or HP enabled.                                 | * |

\*: state at power on initialization

X: reserved: write 0

#### Control Register CR7 Functions (Address: 0x07)

| 7 | 6 | 5 | 4 | 3                     | 2                     | 1                          | 0                          | Function                                                                                                                                                                                                                                                                                   |   |

|---|---|---|---|-----------------------|-----------------------|----------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   |   |   |   |                       | LSA                   | (3:0)                      |                            |                                                                                                                                                                                                                                                                                            |   |

| Х | Х | Х | Х |                       |                       |                            |                            |                                                                                                                                                                                                                                                                                            |   |

|   |   |   |   | 0<br>0<br>0<br>-<br>1 | 0<br>0<br>0<br>-<br>1 | 0<br>0<br>1<br>1<br>-<br>1 | 0<br>1<br>0<br>1<br>-<br>1 | Earpiece / Loudspeaker Amplifier 6 dB gain<br>Earpiece / Loudspeaker Amplifier 4 dB gain<br>Earpiece / Loudspeaker Amplifier 2 dB gain<br>Earpiece / Loudspeaker Amplifier 0 dB gain<br>Earpiece / Loudspeaker Amplifier gain in 2 dB step<br>Earpiece / Loudspeaker Amplifier -24 dB gain | * |

\*: state at power on initialization

X: reserved: write 0

#### Control Register CR8 Functions (Address: 0x08)

| 7 | 6 | 5 | 4                | 3                | 2                | 1                | 0                | Function                                                                                                                                                                                                       |

|---|---|---|------------------|------------------|------------------|------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |   |   |                  | Н                | PLA(4:           | :0)              |                  | T unction                                                                                                                                                                                                      |

| Х | Х | Х |                  |                  |                  |                  |                  |                                                                                                                                                                                                                |

|   |   |   | 0                | 0<br>0           | 0                | 0                | 01               | Headphones amplifier (Left channel) 0 dB gain<br>Headphones amplifier (Left channel) -2 dB gain                                                                                                                |